# GPU-based Acceleration of Radio Interferometry Point Source Visibility Simulations in the MeqTrees Framework

#### RICHARD JONATHAN BAXTER

Dissertation presented for the degree

MASTER OF SCIENCE

in the Department of Computer Science

#### UNIVERSITY OF CAPE TOWN

Supervised by

Dr. Patrick Marais

Assoc. Prof. Michelle Kuttel

## Abstract

Modern radio interferometer arrays are powerful tools for obtaining high resolution images of low frequency electromagnetic radiation signals in deep space. While single dish radio telescopes convert the electromagnetic radiation directly into an image of the sky (or sky intensity map), interferometers convert the interference patterns between dishes in the array into samples of the Fourier plane (UV-data or visibilities). A subsequent Fourier transform of the visibilities yields the image of the sky. Conversely, a sky intensity map comprising a collection of point sources can be subjected to an inverse Fourier transform to simulate the corresponding Point Source Visibilities (PSV). Such simulated visibilities are important for testing models of external factors that affect the accuracy of observed data, such as radio frequency interference and interaction with the ionosphere.

MeqTrees is a widely used radio interferometry calibration and simulation software package that contains a Point Source Visibility module. Unfortunately, calculation of visibilities is computationally intensive: it requires application of the same Fourier equation to many point sources across multiple frequency bands and time slots. There is great potential for this module to be accelerated by the highly parallel Single-Instruction-Multiple-Data (SIMD) architectures in modern commodity Graphics Processing Units (GPU). With many traditional high performance computing techniques requiring high entry and maintenance costs, GPUs have proven to be a cost effective and high performance parallelisation tool for SIMD problems such as PSV simulations.

This thesis presents a GPU/CUDA implementation of the Point Source Visibility calculation within the existing MeqTrees framework. For a large number of sources, this implementation achieves an  $18\times$  speed-up over the existing CPU module. With modifications to the MeqTrees memory management system to reduce overheads by incorporating GPU memory operations, speed-ups of  $25\times$  are theoretically achievable. Ignoring all serial overheads, and considering only the parallelisable sections of code, speed-ups reach up to  $120\times$ .

# Acknowledgements

Like most Masters degrees, this one has a story. It is not necessarily a good one, not excessively exciting or more dramatic than any other story, but a significant chapter in my life. After a stuttering start, this project found a focus in GPU acceleration of radio interferometry image synthesis. After 2 years, I learned of MeqTrees and my topic changed again to the thesis you read here. Although there were greater things planned for this MeqTrees addition, it has been a great experience for me to work on a software suite that will be used by the Square Kilometre Array (SKA) and many other important radio astronomy projects. The characters of this story shaped the unique way in which it unfolded. Whether at the forefront or behind the scenes, major or minor, they cannot go un-thanked.

Assoc. Prof. Kuttel and Dr. Marais have put in too much effort to put all here; thank you for your guidance and support. I also commend the Computer Science Department, especially their administrative staff, for all the outstanding work they do that often goes unnoticed. I would also like to thank Dr. Oleg Smirnov for introducing me to MeqTrees and helping me to create this project. The SKA project, too, has been instrumental in giving me exposure to international scientists via the SKA Postgraduate Conferences and, together with the National Research Foundation, they were vital for my financial well being.

I have to thank my lab mates! As I write this late at night, I am reminded of the many good times we had working into the early mornings. I would also like to thank the students who have come before me, whose work I was able to compare mine to. I only hope that I managed to match up to their high quality. Finally, I would like to thank my friends, my family, my mom and dad and my wonderful partner, Elizabeth; I cannot think how I would have done this without your support.

This has been a marathon, with some difficult hills to climb and some long straights to endure, and although my name is on the front and at the top, I did not do it alone.

# Plagiarism Declaration

I know the meaning of plagarism and declare that all of the work in the document, save for that which is properly acknowledged, is my own.

# Contents

| $\mathbf{A}$ | Abstract               |                                            |     |  |

|--------------|------------------------|--------------------------------------------|-----|--|

| $\mathbf{A}$ | ckno                   | wledgements                                | ii  |  |

| $\mathbf{P}$ | lagia                  | rism Declaration                           | iii |  |

| 1            | Inti                   | roduction                                  | 1   |  |

|              | 1.1                    | Role of High Performance Computing         | 3   |  |

|              | 1.2                    | Aims and Approach                          | 5   |  |

|              | 1.3                    | Contributions                              | 6   |  |

|              | 1.4                    | Thesis Outline                             | 7   |  |

| <b>2</b>     | Bac                    | ckground                                   | 8   |  |

|              | 2.1                    | Radio Interferometry                       | 8   |  |

|              |                        | 2.1.1 Concepts and Definitions             | 9   |  |

|              |                        | 2.1.2 Radio Interferometry Data Pipeline   | 12  |  |

|              |                        | 2.1.3 Simulating Point Source Visibilities | 16  |  |

|              |                        | 2.1.4 MeqTrees                             | 17  |  |

|              |                        | 2.1.5 Parallelism Opportunities            | 18  |  |

|              | 2.2                    | Graphics Processing Units                  | 19  |  |

|              | 2.3                    | Summary                                    | 22  |  |

| 3            | $\mathbf{C}\mathbf{U}$ | DA                                         | 23  |  |

|              | 3.1                    | CUDA Programming Model                     | 23  |  |

|              |                        | 3.1.1 The CUDA Execution Model             | 25  |  |

|              |                        | 3.1.2 CUDA Memory Hierarchy                | 32  |  |

|              | 3.2                    | Thrust                                     | 33  |  |

#### CONTENTS

|   | 3.3 | Genera               | al GPU Optimisation Techniques                      | 35 |  |  |  |

|---|-----|----------------------|-----------------------------------------------------|----|--|--|--|

|   |     | 3.3.1                | Memory-Based Optimisations                          | 35 |  |  |  |

|   |     | 3.3.2                | Processor-Based Optimisations: Occupancy            | 37 |  |  |  |

|   |     | 3.3.3                | Occupancy-Related Considerations                    | 39 |  |  |  |

| 4 | Des | ign and              | d Implementation                                    | 42 |  |  |  |

|   | 4.1 | Proble               | em Definition                                       | 42 |  |  |  |

|   | 4.2 | MeqTr                | rees Execution Model                                | 44 |  |  |  |

|   |     | 4.2.1                | Point Source Visibility Execution Model in MeqTrees | 45 |  |  |  |

|   |     | 4.2.2                | MeqTrees Memory Management                          | 47 |  |  |  |

|   | 4.3 | Thrust               | t Prototype Implementation                          | 47 |  |  |  |

|   | 4.4 | CUDA                 | Design considerations                               | 49 |  |  |  |

|   |     | 4.4.1                | GPU Memory Requirements                             | 51 |  |  |  |

|   |     | 4.4.2                | Shared Memory and Multiple Sources per Thread       | 53 |  |  |  |

|   |     | 4.4.3                | Input and Output Array Indexing                     | 54 |  |  |  |

|   |     | 4.4.4                | Texture and Surface Memory                          | 55 |  |  |  |

|   | 4.5 | CUDA                 | Parallel decomposition                              | 56 |  |  |  |

|   |     | 4.5.1                | Memory allocation                                   | 56 |  |  |  |

|   |     | 4.5.2                | Visibility Kernel                                   | 60 |  |  |  |

|   |     | 4.5.3                | Visibility Kernel Execution Steps                   | 62 |  |  |  |

|   |     | 4.5.4                | Visibility Kernel Tuning                            | 66 |  |  |  |

|   |     | 4.5.5                | Reduction Kernel                                    | 67 |  |  |  |

|   |     | 4.5.6                | Reorder Kernel                                      | 68 |  |  |  |

|   | 4.6 | CUDA                 | Implementation Issues                               | 68 |  |  |  |

|   |     | 4.6.1                | Memory Management                                   | 70 |  |  |  |

|   |     | 4.6.2                | Occupancy                                           | 70 |  |  |  |

|   | 4.7 | Summ                 | ary                                                 | 74 |  |  |  |

| 5 | Eva | Evaluation Methods 7 |                                                     |    |  |  |  |

|   | 5.1 | Code (               | Classification                                      | 76 |  |  |  |

|   |     | 5.1.1                | Timing Metrics                                      | 77 |  |  |  |

|   | 5.2 | Testing              | g Parameters                                        | 79 |  |  |  |

|   |     | 5.2.1                | Experimental Setup                                  | 81 |  |  |  |

| 6 | Res | ults an              | nd Discussion                                       | 83 |  |  |  |

#### CONTENTS

|                  | 6.1   |                                                                                                | 84 |

|------------------|-------|------------------------------------------------------------------------------------------------|----|

|                  | 6.2   | Shared, Surface, and Texture Memory                                                            | 86 |

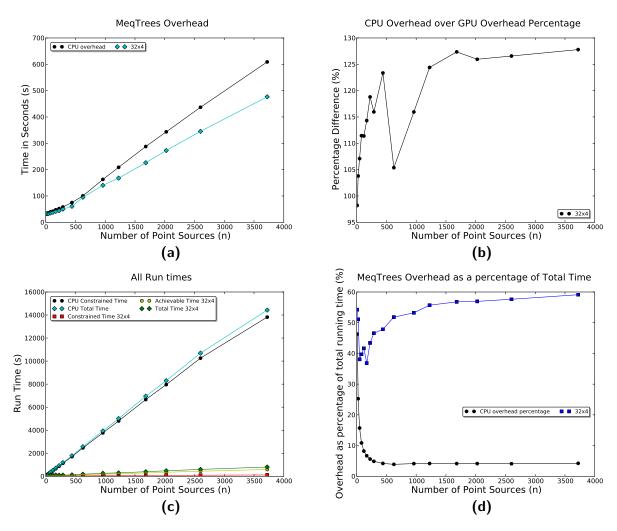

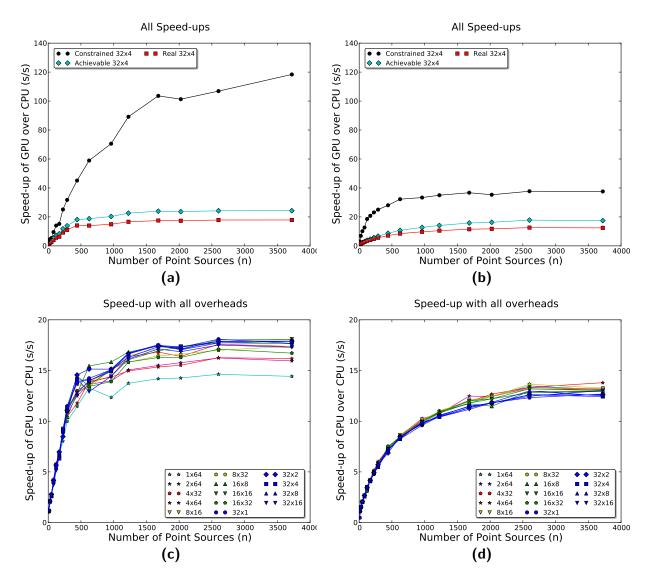

|                  | 6.3   | Impact of MeqTrees Overheads                                                                   | 88 |

|                  | 6.4   | Performance for the WSRT Array                                                                 | 92 |

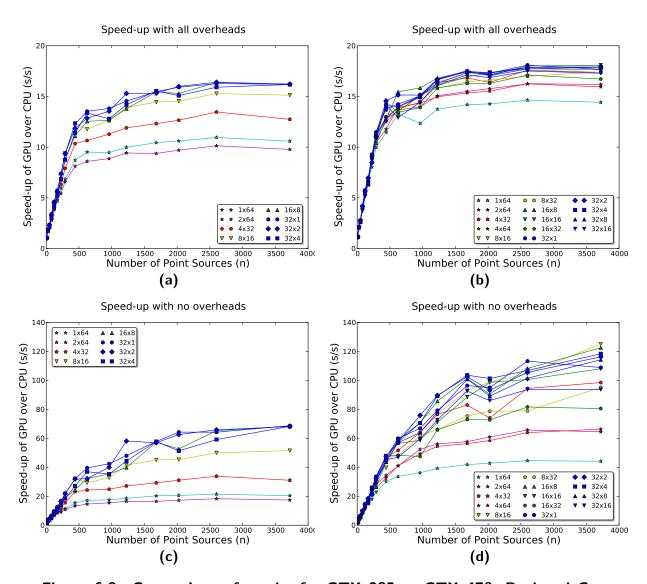

|                  | 6.5   | Effect of Occupancy, L1-Cache, and CC 2.0                                                      | 95 |

|                  | 6.6   | Discussion                                                                                     | 00 |

| 7                | Con   | clusions                                                                                       | 02 |

| $\mathbf{R}_{0}$ | efere | aces 1                                                                                         | 13 |

| $\mathbf{A}$     | Basi  | cs of Interferometry 1                                                                         | 14 |

|                  | A.1   | General Direction                                                                              | 14 |

|                  | A.2   | The Spatial Coherence Function                                                                 | 15 |

|                  |       | A.2.1 The Observed Electric Field                                                              | 15 |

|                  |       | A.2.2 Simplifying Assumptions                                                                  | 15 |

|                  |       | A.2.3 Correlation of the Field                                                                 | 16 |

|                  |       | A.2.4 Spatial Coherence Function                                                               | 17 |

|                  |       | A.2.5 Fourier Inversion of the Spatial Coherence Function of the field $E_{\nu}(\mathbf{r})$ 1 | 19 |

|                  |       | A.2.6 Spherical Measurements Projected onto a Plane                                            | 19 |

|                  |       | A.2.7 Observed Sources Contained in a Small Region of the Sky 1                                | 20 |

|                  |       | A.2.8 The Fourier Transform                                                                    | 21 |

|                  | A.3   | Real World Adjustments and Consideration                                                       | 22 |

|                  |       | A.3.1 Local Adjustments for Angle of Declination                                               | 22 |

|                  |       | A.3.2 Intercontinental Adjustments                                                             | 23 |

|                  | A.4   | The UV-Plane: Larger Arrays and the Rotation of the Earth                                      | 23 |

|                  |       | A.4.1 More-Than-Two Element Arrays                                                             | 26 |

|                  |       | A.4.2 Covering the UV-Plane Using the Rotation of the Earth                                    | 26 |

|                  |       | A.4.3 Declination of Observed Signal                                                           | 30 |

|                  | A.5   | Other Considerations                                                                           | 30 |

|                  |       | A.5.1 Hermitian Nature of the Correlation of the Field:                                        | 30 |

|                  |       | A.5.2 The Sampling Function                                                                    | 30 |

| В                | Poir  | t Source Visibilities 1                                                                        | 34 |

|                  | B.1   | Formulation of the Interferometer Equipment                                                    | 35 |

|                  | B.2   | A single uncorrupted point source                                                              | 35 |

#### CONTENTS

|     | B.2.1 A single corrupted point source    | 137 |

|-----|------------------------------------------|-----|

| В.3 | Multiple sources, times, and frequencies | 137 |

| B.4 | Time and bandwidth smearing              | 138 |

| B.5 | The Final Visibility Equation            | 139 |

# List of Figures

| 2.1 | A dish with a feed horn                                                             | 10 |

|-----|-------------------------------------------------------------------------------------|----|

| 2.2 | The Karoo Array Telescope (KAT-7)                                                   | 11 |

| 2.3 | UV coverage example                                                                 | 14 |

| 2.4 | Example of an intensity map affected by a PSF                                       | 15 |

| 3.1 | CUDA Processing Flow                                                                | 24 |

| 3.2 | Example Grid/Block Layout                                                           | 26 |

| 3.3 | Thread/Block/Grid hierarchy relation to the GPU/SM/SP hierarchy $\ \ldots \ \ldots$ | 28 |

| 3.4 | Example Dual Warp Scheduler                                                         | 30 |

| 3.5 | Coalesced Global Memory Access                                                      | 34 |

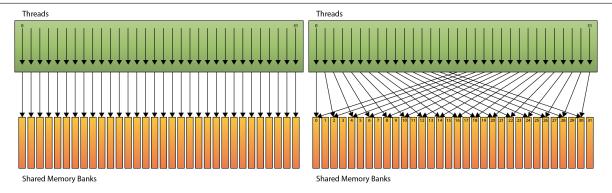

| 3.6 | Shared Memory Banked Access                                                         | 37 |

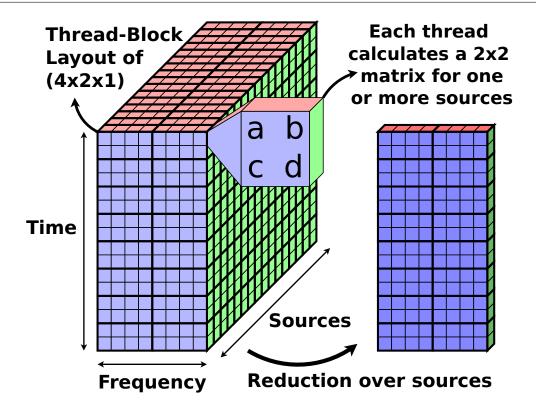

| 4.1 | Visual representation of the PSV data-cube                                          | 44 |

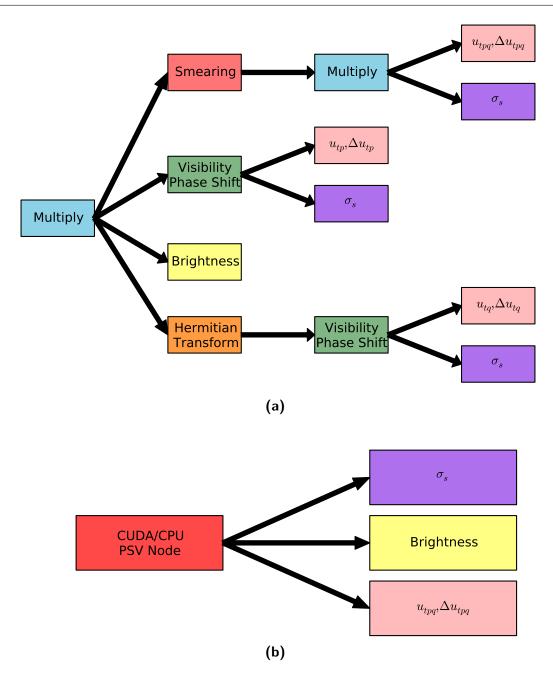

| 4.2 | GPU/CPU PSV Measurement Equation Trees                                              | 46 |

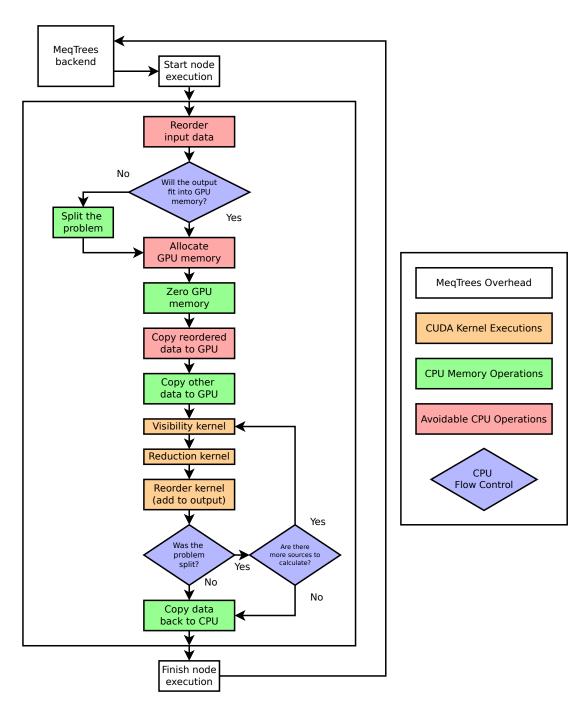

| 4.3 | Flowchart of the execution of the PSV node                                          | 57 |

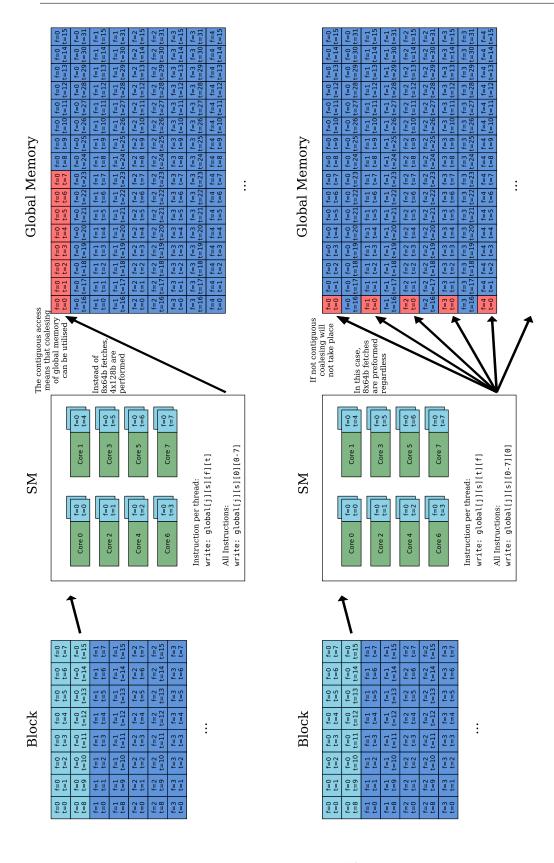

| 4.4 | How reordering data affects memory access patterns                                  | 59 |

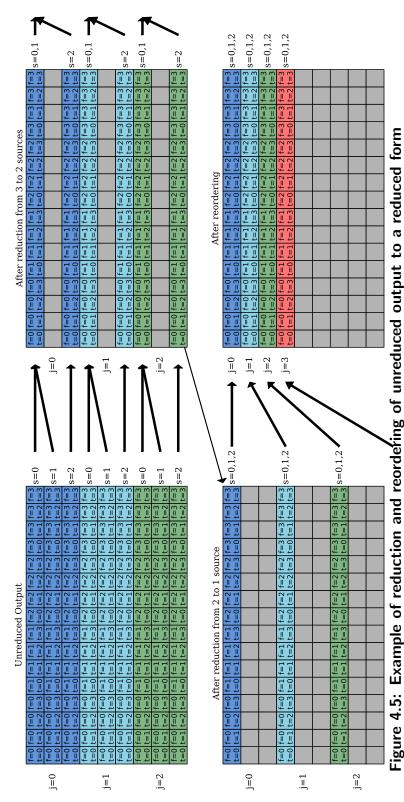

| 4.5 | Example of reduction and reordering of unreduced output to a reduced form           | 69 |

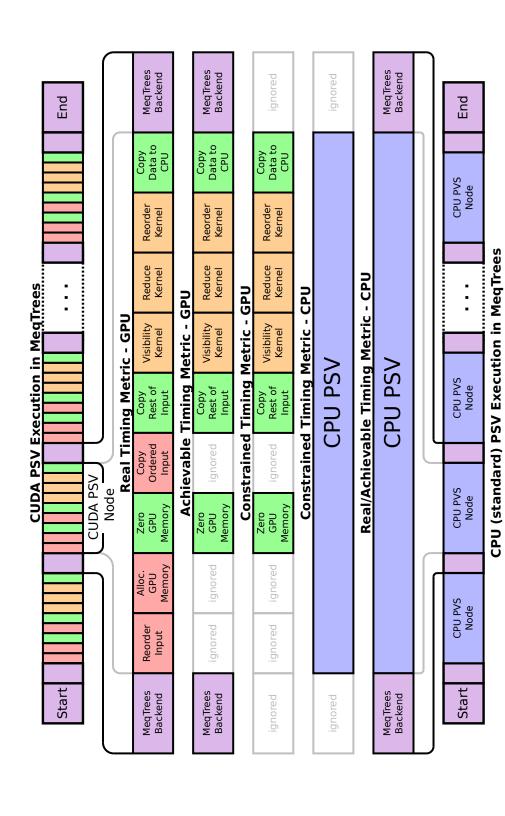

| 5.1 | Breakdown of the different timing metrics used in a MeqTrees simulation run.        | 78 |

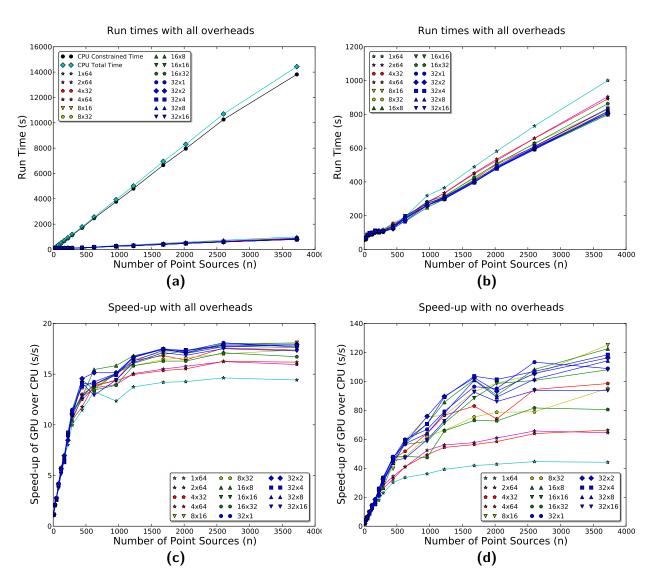

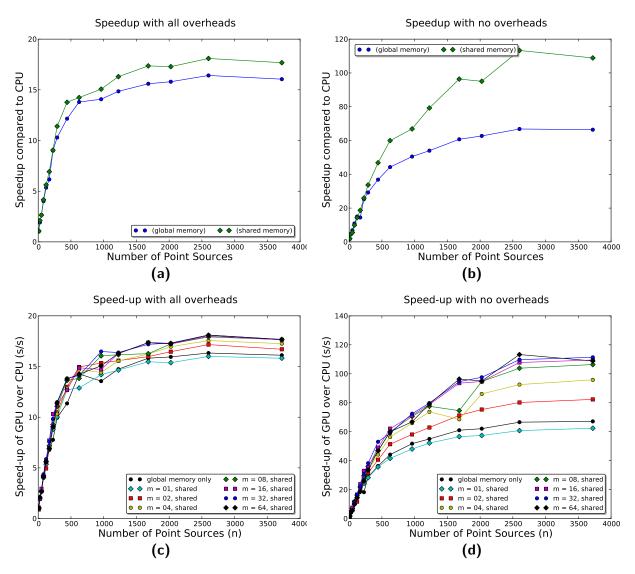

| 6.1 | Real and Constrained Run Times and Speed-ups for all thread-block layouts           |    |

|     | (MeerKAT array, nVidia GTX 470)                                                     | 85 |

| 6.2 | Comparison of speed-up relative to CPU for shared memory versus global              |    |

|     | memory (MeerKAT array, n<br>Vidia GTX 470 & Intel i<br>5 $2.66\mathrm{GHz})$        | 87 |

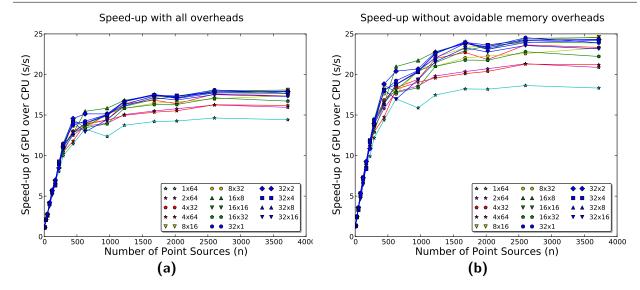

| 6.3 | Real and $Achievable$ speed-ups for all thread block layouts (MeerKAT array,        |    |

|     | n<br>Vidia GTX 470 & Intel i<br>5 $2.66 {\rm GHz})$                                 | 88 |

#### LIST OF FIGURES

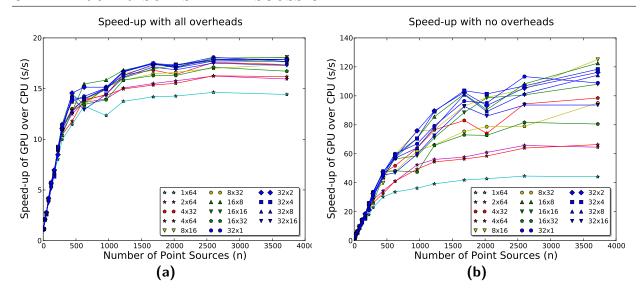

| 6.4 | Real and Constrained speed-ups for all thread-block layouts (MeerKAT array,        |     |

|-----|------------------------------------------------------------------------------------|-----|

|     | n<br>Vidia GTX 470 & Intel i<br>5 $2.66 {\rm GHz})$                                | 89  |

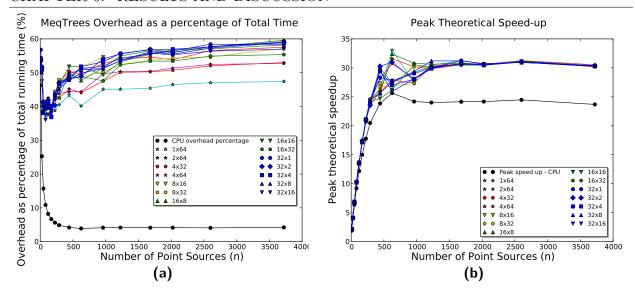

| 6.5 | Percentage time of MeqTrees overhead compared to total running time (MeerKA)       | Γ   |

|     | array, nVidia GTX 470 and Intel i5 2.66GHz)                                        | 90  |

| 6.6 | Discrepancy between CPU and GPU overheads                                          | 91  |

| 6.7 | Speed-ups of PSV calculations with the smaller Westerbork Synthesis Radio          |     |

|     | Telescope compared to the MeerKAT array (WSRT array/MeerKAT array,                 |     |

|     | nVidia GTX 470 versus Intel i5 2.66GHz)                                            | 94  |

| 6.8 | Effect on speed-up of 16kB versus 48kB shared memory configuration (MeerKAT        |     |

|     | array, nVidia GTX 470 and Intel i5 2.66GHz)                                        | 98  |

| 6.9 | Comparison of results for GTX 285 vs GTX 470, Real and Constrained speed-          |     |

|     | up (MeerKAT array, n<br>Vidia GTX 285/GTX 470 and Intel i<br>5 $2.66\mathrm{GHz})$ | 99  |

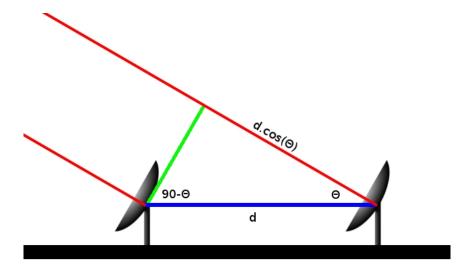

| A.1 | Affect of declination on time delay in receiving signal                            | 122 |

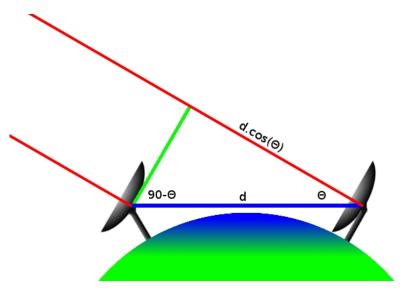

| A.2 | Affect of earth's curvature on time delay in receiving signal                      | 123 |

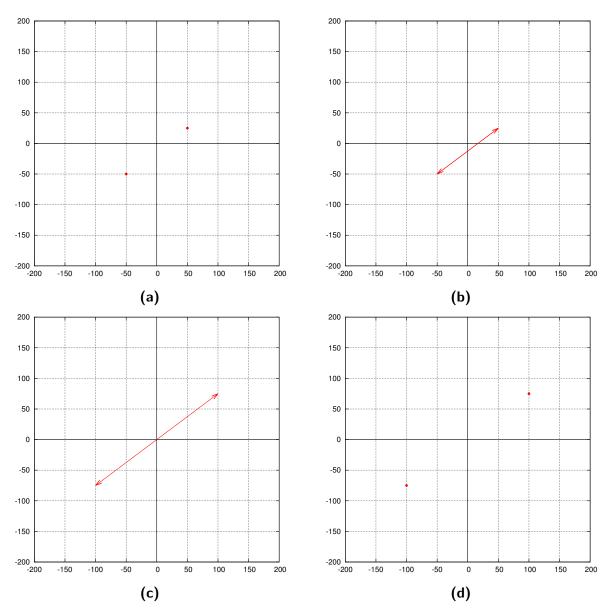

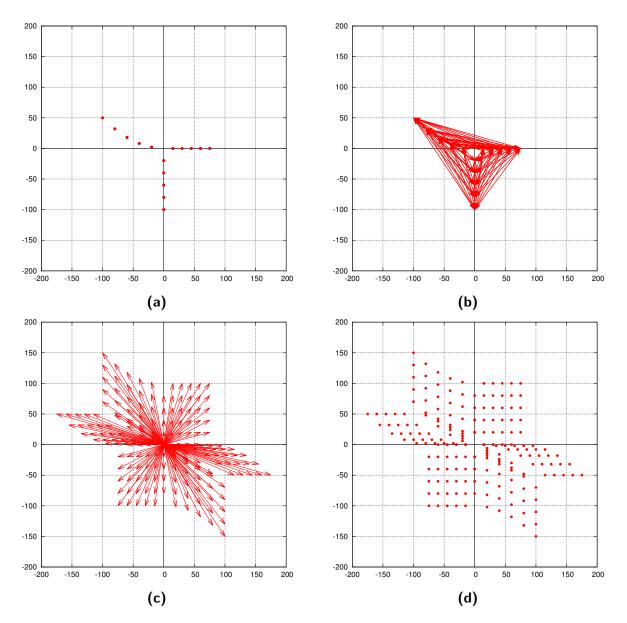

| A.3 | A UV-plane of a 2 element interferometer                                           | 125 |

| A.4 | A UV-plane of a 3 element interferometer                                           | 127 |

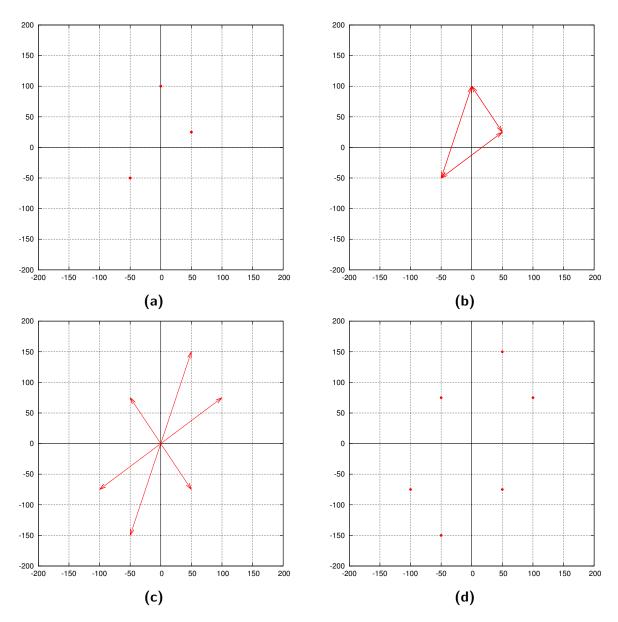

| A.5 | A UV-plane of a 15 element interferometer                                          | 128 |

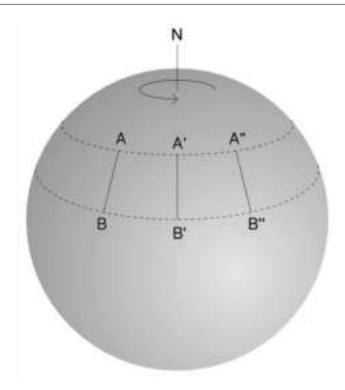

| A.6 | A simple example of the effect of the earth's rotation                             | 129 |

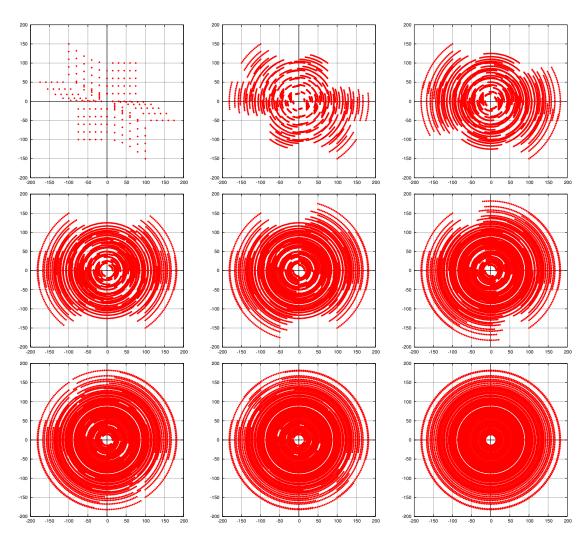

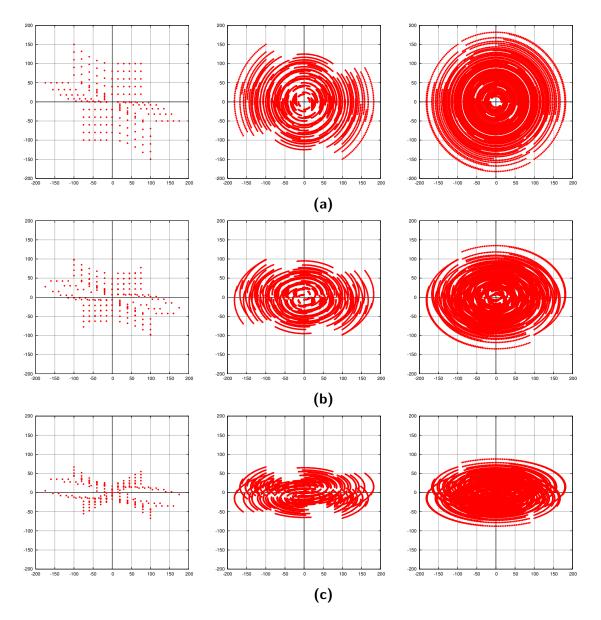

| A.7 | The UV-distribution over time                                                      | 132 |

| A.8 | A demonstration of the UV-plane at different declinations                          | 133 |

# List of Tables

| 3.1 | Compute Capability Specific Specifications                          | 29 |

|-----|---------------------------------------------------------------------|----|

| 3.2 | CUDA Memory Types                                                   | 32 |

| 4.1 | Dimensions of Input and Output Vectors                              | 54 |

| 4.2 | Effect of Different Configurations on Occupancy                     | 72 |

| 6.1 | Running times per time slot group per pair (MeerKAT and WSRT array, |    |

|     | nVidia GTX 470 versus Intel i5 2.66GHz)                             | 95 |

| 6.2 | Effect of occupancy on speed-up                                     | 96 |

# List of listings

| 3.1 | Example CUDA Kernel                                   | 27 |

|-----|-------------------------------------------------------|----|

| 4.1 | Python-style pseudo-code of PSV execution in MeqTrees | 45 |

| 4.2 | Thrust PSV Functor                                    | 50 |

| 4.3 | Simplified visibility kernel code                     | 63 |

# Chapter 1

## Introduction

Radio interferometry is the use of multiple radio-receiving elements (traditionally radio dishes, but also can be individual dipoles or phased array stations) to enhance the resolution and sensitivity of astronomy observations. While single dish telescopes convert the electromagnetic radiation directly into an image of the sky (known as the sky intensity map), interferometers calculate the interference patterns between pairs of receiving elements to produce sample points on the Fourier-plane (termed visibilities). A subsequent Fourier transform operation on a collection of samples produces the sky intensity map (Thompson et al., 2009). This process is called image synthesis.

The reverse process (conversion from a sky intensity map into the corresponding Fourier-plane visibilities) allows one to simulate what visibilities would be obtained given a certain sky model and model of instrumentation distortions as well as other effects (e.g. atmospheric effects and radio interference). This step is vital in the *fitting loop* of interferometer calibration, whereby a simulation is repeatedly run with model parameters to obtain a best fit to the data (and thus a best fit to the model parameters). A sky intensity map comprising a collection of point sources (a source is simply an observable entity in the sky) may be transformed into the corresponding point source visibilities with an inverse Fourier transform (Smirnov, 2011d). This process is called a visibility simulation in general, and a point source visibility simulation when a point source sky map is used.

Both the image synthesis and visibility simulation calculations — i.e. from visibilities to sky intensity map and from sky intensity map to visibilities — require direct Fourier transforms. This is computationally demanding as each pixel/visibility must undergo a Fourier transform.

#### CHAPTER 1. INTRODUCTION

For example, computation of a modest  $256 \times 256$  pixel image from 1,000,000 visibility samples requires 256 \* 256 = 65,536 Fourier transform calculations for *each* of the samples. The reverse (simulation) process, from an image model to visibility samples, involves a similar number of operations. Using a point source model of the sky to simulate 1,000,000 visibility samples from a model comprising of 4000 point sources requires the computation of  $4 \times 10^9$  Fourier transforms.

Extant interferometers comprise anywhere from 6 (21 base-line pairs) to 30 elements (465 base-line pairs): the Australia Telescope Compact Array has 6 elements (McKay and Wark, 2009); the Westerbork Synthesis Radio Telescope (WSRT) in the Netherlands has 14 elements (ASTRON, 2012a); the Very Large Array in New Mexico, USA has 27 elements (Associated Universities Inc. 2012), and the Giant Meterwave Radio Telescope (GMRT) in India with 30 elements (NCRA-TIFR). The LOW Frequency ARray (LOFAR) in the Netherlands has somewhat different architecture, comprising a phased array set up of 20,000 small, cheap antennas, grouped into 40 stations (780 base-line pairs) (ASTRON, 2012b). The next generation of interferometers will be considerably larger: the Australian Square Kilometer Array Pathfinder (ASKAP) is tabled to comprise 36 elements (CSRIO, 2012); the Allen Telescope Array in California, USA, currently has 42 elements and is planned to extend to 350 antennas at completion (SETI Institute, 2012); and the MeerKAT Array in South Africa will have 64 elements (Horrell, 2012). The Square Kilometer Array (SKA) is likely to comprise both a phased array interferometer and a traditional dish interferometer with "an estimate of 2000 - 3000 ... antennas" (Dewdney et al., 2011). At 4.5 million base-line pairs, this will present a significant computational challenge.

The standard, well-explored, acceleration solution for Fourier transform calculations is to utilise the Fast Fourier Transform (FFT) algorithm. The FFT is one of the most widely-used computer algorithms in the scientific world and accelerates discrete Fourier transform calculations, reducing the complexity from  $\mathcal{O}(N^2)$  to  $\mathcal{O}(N \log N)$  (Cooley and Tukey, 1965; Brigham and Morrow, 1967). For image synthesis, a two-dimensional FFT is used to convert the visibilities into an image (Nussbaumer, 1982; Thompson et al., 2009), whereas current visibility simulation software still uses the computationally expensive direct Fourier transform method (Smirnov, 2012).

## 1.1 Role of High Performance Computing

Given its high computational cost and the lack of inter-dependencies in the input data, visibility simulation is a clear candidate for exploitation by High Performance Computing (HPC) and parallel processing technologies. The high computational load limits the complexity of the simulation, as only simple point source maps can be run in reasonable time. With the application of HPC technologies, these simulations can be accelerated, allowing for more testing of more complex and realistic models in shorter time frames.

The traditional HPC system is a cluster, with inter-connected CPU nodes, each responsible for a fraction of the total processing load. More recently, vector streaming systems such as as Cell (Gschwind, 2006), ClearSpeed (ClearSpeed Technology Ltd, 2012; Kozin, 2009) and MD GRAPE (IBM Research; SGI Japan), as well as GPU (Graphics Processing Unit) technology, have been developed as alternative parallel computing solutions. Instead of using a large number of serial processors that each perform one instruction on one register per clock cycle, vector processors are able to perform one instruction on multiple registers simultaneously with each clock cycle.

We focus on the GPU, the modern evolution of the graphics card. Like vector stream processors, a GPU can perform operations simultaneously on multiple data inputs using its many compute cores. In the past, these processors would only be able to perform specific rendering operations and specific 3D geometry transformations, which allowed 3D vertex information to be transformed into 2D screen coordinates. Later these processors were extended into programmable shaders which allows a programmer to chose how a vertex would be transformed. Shader-based graphics cards would often have multiple shader processors running in parallel to improve performance. Attempts to leverage these parallel shader processors to do general purpose computation on the GPU (GPGPU) were successful; however, the computation was always akin to fitting a square peg into a round hole, as general code must be written in the guise of rendering operations. On modern GPUs, these disparate shader processors were eventually unified into a single, more general, type of processor that could subsume the all of the shader tasks. Current high-end GPUs consist of over 512 cores and are able to execute general code on each of these cores in parallel.

GPUs fall into into the *Single-Instruction-Multiple-Data* (SIMD) paradigm, meaning that there is a single task that is to be applied to many data points. This is in contrast to Multiple-Instruction-Multiple-Data (MIMD) paradigm, which is applicable to problems within which

#### CHAPTER 1. INTRODUCTION

there are many different tasks to be performed on many different data points (Patterson and Hennessy, 2008). The direct Fourier transform in PSV simulations is a SIMD problem, as the same Fourier calculation must be performed on all the data points. As such, it should benefit from SIMD technologies such as vector stream processors and GPGPU (General Purpose computing on the GPU) technologies. Vector stream processors are effective at parallelising SIMD problems, but often have high entry and maintenance costs (Matsuoka et al., 2009). GPGPU technologies utilise commodity graphics hardware and offer a far more cost effective solution.

Currently leading the industry in GPU technology is nVidia and AMD, each with their own GPGPU software and hardware. nVidia's Compute Unified Device Architecture (CUDA) features a compiled high-level, C-like language for computation on their modern GeForce GPUs, whereas AMD (previously ATI) released a low-level language, FireStream, for general computation on their Radeon GPUs (AMD, 2010). AMD's current GPU efforts are focused mainly on OpenCL (Open Compute Language). OpenCL is a language interface which allows for a single piece of code to run on many different HPC hardware systems (Munshi, 2011). To date, both nVidia and AMD have OpenCL implementations, allowing for OpenCL utilisation on both vendors' hardware (Karimi et al., 2010). While OpenCL has improved significantly in recent years, and looks to become the leading platform for heterogeneous computing, CUDA remains the more prominent technology owing to its faster execution times, mature API, and wide support in the form of libraries and tools (Karimi et al., 2010).

Given the need for an accelerated implementation of PSV computation, and the wide acceptance of CUDA, we have developed a CUDA version of the PSV model present in the leading astronomy software suite, MeqTrees (Noordam and Smirnov, 2011). Our implementation exploits the SIMD nature of the PSV calculations with commodity graphics hardware, thus allowing a computationally effective and cost-effective parallelisation solution.

The MeqTrees framework has been developed to compute any *Measurement equation* by defining the equation as a *Tree*. It can perform a wide variety of computations (represented as trees) and is defined by a simple Python script (Noordam and Smirnov, 2011). Its main purpose is to perform third generation calibration (3GC). In practice, recorded visibilities are subject to corruption by instrumental effects (these corruptions can be represented as per-antenna complex gain terms — i.e. an amplitude and a phase per antenna — that varies with time and frequency but not with direction). Calibration attempts to solve for these effects, and to recover the true visibilities. First generation calibration (1GC) techniques

involve switching from observations of the target with those of a known calibrator source and then back. Second generation calibration (2GC) solves for per-antenna complex gains and the unknown target sky region simultaneously, without having to break observation of the target to externally calibrate. 3GC techniques extend this with the ability to take direction-dependant gains into account. With each generation, the achievable signal-to-noise ratios of interferometers increased as well, improving sensitivity of the data. MeqTrees is designed to be flexible to allow for a multitude of 3GC instrumental and interference models (Noordam and Smirnov, 2011).

Within its many modules, MeqTrees includes a PSVs module. This module produces a simulated UV-plane based on a number of input data: interferometer setups, instrumental models, noise models and sky map models. This is essentially a simulated interferometer, and can be used to evaluate and improve the aforementioned models and for simulation in of itself. As mentioned above, however, PSV simulation is computationally intensive as it utilises a direct Fourier transform method.

## 1.2 Aims and Approach

The principal goal of this work is to accelerate PSV calculations performed by the current CPU PSV component of the MeqTrees framework. We aim to achieve this by exporting the CPU PSV component to the SIMD parallel architecture on modern GPUs. To enable comprehensive parallel optimisation, we focus on nVidia's CUDA devices and our code and we integrated our code into the execution paradigm of the MeqTrees software package.

We port the computational parts of the PSV module into a new CUDA PSV module, which we add to the MeqTrees framework, leaving the remainder of the framework unchanged. For the CUDA PSV module, we create a naive implementation, and then iteratively add common CUDA optimisation techniques to determine their efficacy. In particular, we explore methods to reduce the amount of off-chip memory accesses, methods such as effective use of CUDA shared memory and exploitation of CUDA memory coalescing via optimal thread organisation. We also explore processor utilisation to determine its importance in accelerating this computation. Data-sets of multiple sizes are used with two distinct interferometer setups, namely the Westerbork Synthesis Radio Telescope and the MeerKAT (Karoo Array Telescope), the Square Kilometre Array (SKA) pathfinder.

#### CHAPTER 1. INTRODUCTION

Performance of the new CUDA PSV module is benchmarked against the CPU version, to determine the magnitude of performance gain achieved by the CUDA GPU. To determine the effect that each optimisation has on the final speed-up, various CUDA optimisations are selectively removed and the code is benchmarked against the CPU version as well as other GPU versions. These benchmarks are analysed to determine the best configuration of optimisations for optimal memory and processor performance. We run our tests on nVidia's commodity Fermi architecture under numerous configurations and compare it to older hardware to gain insight as to what technological advancements in the newer hardware are most effective (such as off-chip memory caching and increased double precision floating point operation throughput).

#### 1.3 Contributions

The main contribution is the creation of a node in MeqTrees that utilised the processing power of the GPU and the fact that it performed significantly faster than its CPU counterpart. Although it is only a working prototype of a CUDA MeqTrees node, it can be incorporated fully into the MeqTrees code-base with some additional work. This was achieved by implementing and optimising a CUDA PSV node, and discovering what technical challenges there are for future attempts at implementing GPU functionality in MeqTrees.

This work notes the importance of the use of shared memory to reduce off-chip memory accesses. The PSV problem is characterised by relatively small input vectors in comparison to the output vectors. The actual process involves a large amount of GPU memory for intermediate values, which are reduced to a smaller final output vector. Shared memory allows us to do part of the reduction in on-chip memory before it is written to off-chip memory, thus reducing off-chip memory writes significantly.

It is found that the serial (hence not parallelisable) section of the code becomes the main bottleneck for accelerating the PSV node. It is a primary point to be taken from this work that acceleration of the core computations alone will result in at most an order of magnitude reduction in total running time, even if the core computation is sped up a thousand fold or more. The reason behind this is that the previously small fraction of the MeqTrees overhead becomes hinderingly significant when the core computations are accelerated. Whilst this overhead is a result of MeqTrees' flexibility and wide scope, in order to achieve speed-ups of more than two orders of magnitude, this overhead should be parallelised or accelerated in

some manner.

Massive radio interferometers such as the SKA will have computational requirements multiple orders of magnitude larger than any previous interferometer. These projects will have sensitivity far exceeding anything before them, and thus will require even more precise and accurate calibration models so as to improve signal-to-noise ratio. RFI has always been a primary concern, but with 3GC calibration techniques, the need to test atmospheric interference has become just as important, as scientists and engineers strive towards better, more sensitive equipment. PSV simulations allow for testing and acceleration of these models, which enable faster turnaround and more complete simulations.

#### 1.4 Thesis Outline

The thesis is structured as follows:

Chapter 2 reviews the basics of Radio Interferometry (specifically Point Source Visibility calculations), GPGPU technology (specifically CUDA technology) and relevant Fourier transforms, and explores the surrounding literature.

Chapter 3 explains the CUDA programming and hardware models, CUDA implemented Thrust library, and common CUDA optimisation techniques.

Chapter 4 details the techniques with which the PSV node in MeqTrees is implemented. It also outlines how MeqTrees defines equations as expression trees and specifically how PSVs are defined. Furthermore, it explains the MeqTrees execution model and how the GPU node is incorporated.

Chapter 5 details how results are measured, the metrics used and the experimental setup. Chapter 6 shows the findings of these tests with discussions thereof. Conclusions and future work are presented Chapter 7.

The Appendices present detailed explanations of image synthesis in radio interferometry (A) and PSVs (B). These support the main body of the thesis and are referred to throughout.

# Chapter 2

# Background

This chapter serves to give the reader the understanding of radio interferometry and GPU technology required to follow the remainder of the thesis. Radio interferometry and related concepts are defined and the radio interferometry data pipeline is outlined with an emphasis on the computational challenges that it presents. The MeqTrees framework, a central component to this work, is then introduced. The evolution of GPGPU technology is summarised in the context of High Performance Computing (HPC) technology. Furthermore, CUDA and CUDA-related technologies are introduced. An overview of some literature (especially pertaining to GPGPU technology in astronomy) is discussed in this chapter, but related literature is largely contained in the relevant chapters.

## 2.1 Radio Interferometry

Radio interferometry is the use of multiple radio-receiving elements to enhance the resolution and sensitivity of astronomical observations by measuring interference patterns between receiving elements. This contrasts with traditional single dish telescopes that convert the electromagnetic radiation directly into an image of the sky (or sky intensity map).

An interferometer measures *visibilities*, which are samples of the Fourier transform of the sky intensity map, by correlating the signals received by each element with every other element in the array. The interferometer will measure many visibilities in a snapshot observation, or over a number of hours. When plotted on the same plane, the set of visibilities produces a sampled Fourier plane of the observed region of the sky. An inverse Fourier transform (either

a direct Fourier transform or a Fast Fourier Transform (FFT)) then produces the desired observed sky intensity map.

The reverse process of producing (or simulating) visibilities from a model sky intensity map is primarily used for testing various instrumental distortion models and thereby increasing the signal to noise ratio and improving sensitivity.

#### 2.1.1 Concepts and Definitions

A radio wave is electromagnetic radiation with a long wavelength, above 1mm and include 1 meter and even 1 kilo-meter wavelengths. Unlike optical signals that operate on shorter wavelength and can be measured by reflecting and focusing electromagnetic radiation signals by use of a reflective surface or by refracting the signal using a transparent (glass) lens, radio waves are measured by focusing the signals into a receiver with large paraboloid dishes. Since longer wavelengths reduce resolution, larger collecting areas are necessary to maintain an acceptable resolution, as given in the following linear proportion:

$$R \propto \lambda/D$$

(2.1)

where R is the angular resolution in radian,  $\lambda$  is the wave-length, and D is the diameter of the collecting surface (the dish). This phenomenon is referred to as the diffraction-limit, as the resolution is limited by the diffraction of light, which at larger wavelengths, is worse. The resolution in this case is angular since signals are received over a spherical sector of the sky. The definition of angular resolution is the minimum angular distance to resolve (distinguish) two point sources as distinct object, as opposed to pixel density. A lower R is equivalent to an increase in pixel density. An increases diameter increases resolution, but also decreases the Field-of-View (FoV).

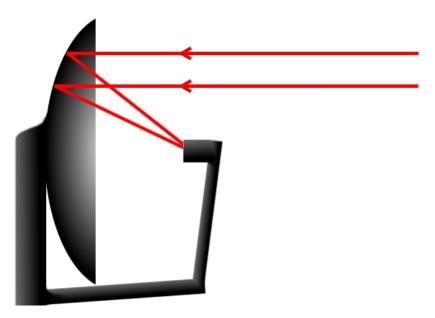

In order to obtain a high enough resolution, larger and larger radio telescopes have been manufactured in a variety of shapes. All dishes, however, essentially reflect and focus electromagnetic radiation onto a receiver, which then digitises the signal (Figure 2.1).

To date, the largest steerable radio telescopes in the world are about 100m in diameter, such as the Effelsberg 100m Radio Telescope and the slightly larger than 100m Green bank Telescope. The largest telescope is located in Arecibo, Puerto Rico; it is 305m in diameter, but is built in a natural sink-hole and is thus immovable. Currently under construction in

**Figure 2.1: A dish with a feed horn** *Incoming rays are reflected and focused onto a feed-horn, which converts the signal to a voltage.*

Pingtang County, China is the Five hundred meter Aperture Spherical Telescope (FAST), built in a natural basin. All of these very large dishes, regardless of mobility, are costly to build and maintain. The engineering and monetary requirements for creating significantly larger dishes are becoming more and more infeasible with each advancement. It is thus unlikely that higher resolution images can reasonably be obtained by simply building larger dishes.

Another method for obtaining an effective larger collecting area is to use an array of smaller telescopes (as shown in 2.2) rather than a single large one. This method, known as *interferometry* or *aperture synthesis*, measures the interference patterns between dishes and allows synthesis of a telescope with an aperture equal to the greatest distance between telescopes. This changes Eqn 2.1 to:

$$R \propto \lambda/B$$

(2.2)

where R is the angular resolution,  $\lambda$  is the wave length, and B is the longest baseline of the array. The longest baseline of an array of telescopes is the longest distance between any two telescopes. Whilst there do exist optical interferometers, interferometry is most effectively used for radio signals owing to the difficulty in accurately measuring interference patterns

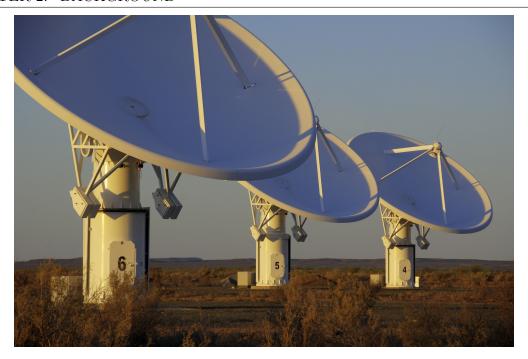

Figure 2.2: The Karoo Array Telescope (KAT-7)

The KAT-7 consists of seven identical 12m parabolic dishes. This array is the testbed upon which the 64 dish MeerKAT array is currently being built. (SKA South Africa, 2012; Wolleben, 2012)

in shorter wavelength signals.

Since an interferometer consists of many small dishes that can be placed far apart from each other, it has the great advantage of being able to produce higher resolution images than the traditional single dish method (see Appendix A for more details). Another advantage is that an interferometer will have a FoV based on the diameter of the individual dishes, even though the resolution is related to the longest baseline. Increase FoV means that more of the sky can be surveyed at a time, and speeds up observation time proportionately.

Unfortunately, since interferometers measure interference patterns between pairs of antennae rather than direct signals. the number of pairs in an N element interferometer is given by:

$$\frac{(N-1)N}{2} \tag{2.3}$$

As such, additional processing is required to transform the interferometer output into usable data. A notable disadvantage here is that this additional processing is very computationally expensive and may require HPC technologies in order for the interferometer to serve as a

feasible observational tool.

Whilst two telescopes of an interferometer can be placed very far apart from each other to increase resolution, the total collecting area is still very small thus limiting sensitivity. More telescopes in an interferometer array increases its total collecting area, which increases sensitivity, but increasing the number of elements also increases the computational cost.

Specifically, the computational cost is quadratic with respect to the number of elements in the array, since an interferometer measures interference between each *pair* of elements 2.3. The distance between the elements are called baselines. Any two elements constitute a baseline pair. For new and upcoming interferometers with increasing numbers of array elements, the computational cost grows significantly faster than the size of the array.

#### 2.1.2 Radio Interferometry Data Pipeline

As an interferometer measures the interference patterns between pairs of antennae, there is not a simple direct path from received signal to the analysed data. Thus a data pipeline has developed and is as follows:

- 1. The array of telescopes collect their respective signals and are combined in a correlator to produce a set of *visibilities* over a number of hours

- 2. These visibilities are then transformed into an image of the sky using a Fourier transform. This results in a image of the sky convolved with the interferometer's Point Spread Function (PSF)

- 3. This image then undergoes some post-processing to remove the convolution in a process called *deconvolution*.

- 4. A second phase of post processing is sometimes performed to remove background noise in the data.

- 5. Data is analysed

Each pair of receiving elements collects one *visibility* or UV-sample over typically 0.1 to 30 seconds. Longer sample times means that more signal is received per sample, increasing sensitivity, but also means there are fewer visibilities for the observation, which leads leads to a more sparsely sampled Fourier domain and reduced ability to measure short term variability in the observed source owing to time and bandwidth smearing (see Appendix B.4). Samples

sets are collected over a few hours of observation. To give some indication of the sheer amount of visibilities that are collected, consider a modest 16 element interferometer that samples every 10 seconds over 8 hours (or 28,800 seconds). According to Eqn 2.3, this is  $\frac{16*15}{2} = 120$  pairs, each collecting over  $\frac{28,800}{10} = 2,880$  time-steps, totalling 345,600 samples.

The number of antenna pairs grows quadratically with the number of antennae. If we, in our example, double the number of elements to 32, then the number of pairs would increase to 496, over four times the original of 120. The number of samples increases to 1,428,480 visibilities. Thus, as interferometers become larger, the computational cost becomes increasingly significant. Compounding this, advances in radio dish technology, such as increased sensitivity and reduced internal noise, allow for shorter sampling times and hence more samples per baseline pair per hour. With modern interferometers reaching over 60 elements (1770 pairs) and considering typical observing conditions of 1 second samples over 10 hours (36000 sample sets), the number of samples can balloon to over 60 million. With future interferometers like the SKA, which should contain a few thousand elements, the computational challenge becomes substantially more significant.

Adding to this already large number of visibilities, multiple frequency channels are often measured simultaneously, typically 32 or 64 channels at a time. Thus 32 or 64 times the number of visibilities. The number of visibilities recorded in an observation is

$$S = \frac{N(N-1)}{2} \times f \times t$$

where N is the number of elements in the array, f is the number of frequency channels and t the number of time-steps taken.

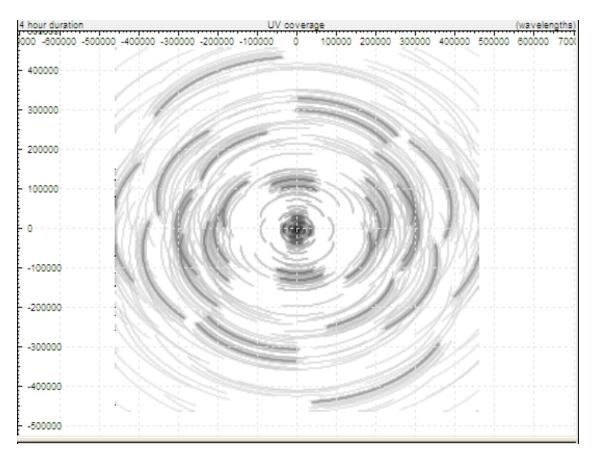

Mathematically, a plot of all the visibilities (called the *UV-plane*) is equivalent to a sampled version of the Fourier plane (see Figure 2.3 for an example). Thus a Fourier transform of the UV-plane results in the image plane, or *sky intensity map*. Appendix A has a detailed overview of visibility collection and the underlying mathematics.

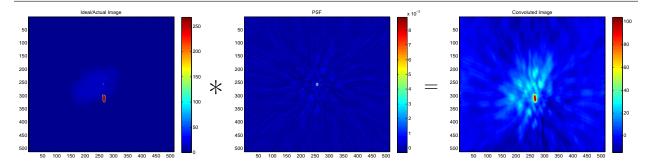

Although a Fourier transform of the UV-plane reconstructs the sky intensity map (Figure 2.4, left), the reconstruction is not perfect. The actual reconstruction is the observed signal convolved with the interferometer's PSF (Figure 2.4, right). Whilst in optical telescopes the PSF usually has a 2D Gaussian shape, the PSF of an interferometer is dependent of the UV-plane distribution (PSF shown in Figure 2.4, middle) which is dependent on array layout and the length of time over which the observation was performed. As such, the reconstruction is

Figure 2.3: UV coverage example

UV coverage of a four-hour observation with the LOw Frequency ARray (LOFAR). While it covers a large area, there are still many gaps between the samples. If this plane were to be filled/fully sampled it would represent the Fourier Inverse of the observed sky intensity map.

called the dirty image.

This dirty image is then 'deconvolved' to produce a *clean image*. Internal instrumentation noise, as well as other noise caused by non-observational effects corrupts the post-convolution signal, means a straightforward inverse convolution greatly amplifies this internal noise and makes the deconvolved image unusable <sup>1</sup>. Thus, approximate or heuristic deconvolution algorithms are found to be more effective, and is a field of study in its own right (Taylor et al., 1999). We do not investigate or implement deconvolution in this thesis.

The most widely used technique for producing the dirty image is to re-sample the Fourier

<sup>&</sup>lt;sup>1</sup>Internal noise in this context is strictly undesirable local noise and not background observational noise. Background noise from other sources in the sky will be preserved by a direct inversion.

Figure 2.4: Example of an intensity map affected by a PSF

Left: Actual Intensity map of the sky. Middle: Point spread function of the interferometer.

Right: The convolution of the two. This is the data that the interferometer produces (minus any noise).

samples onto a uniform grid and then perform a Fast Fourier Transform (FFT) (Thompson et al., 2001). For image synthesis, a two-dimensional FFT (2D FFT) is used to convert the visibilities into an image (Nussbaumer, 1982; Thompson et al., 2009). Since the FFT requires discretised data, the visibilities are discretised (or 'gridded') such that they lie on a uniform grid. This usually involves some form of transformation or convolution function (Sault and Wieringa, 1994; Rau et al., 2009; Thompson et al., 2009).

Using an FFT is faster than calculating the direct Fourier transform on a per-sample basis. To demonstrate the difference in computational complexity, consider a data set of S samples. Using a per-sample transform based on a direct Fourier transform, an  $M \times M$  image ,where M represents the pixel dimensions of the image, must be calculated for each of the S samples, which requires  $\mathcal{O}(M^2)$  running time per sample —  $\mathcal{O}(M^2S)$  in total. These S images are summed (or reduced) to a single image; this operation also has a running time of  $\mathcal{O}(M^2S)$ .

For the direct Fourier transform (non-FFT) method of image synthesis, we need to calculate P pixels:

$$P = \frac{N(N-1)}{2} \times M^2 \times f \times t$$

where N is the number of elements in the array, f is the number of frequency channels, and t the number of time-steps taken.

The visibilities can be discretised onto a uniform  $M \times M$  grid/image using an FFT. The FFT algorithm runs in  $\mathcal{O}(N \log(N))$  for a data set of N values. An FFT on a 2D  $N \times M$  data set is equivalent to performing N 1D FFTs on each of the rows (each row an M-length vector) and then M 1D FFTs on each column (each column an N-length vector). This operation

requires a  $\mathcal{O}(M \cdot N \log(N) + N \cdot M \log(M)) = \mathcal{O}(MN \log(MN))$  running time.

A 2D FFT on an  $M \times M$  grid would run in  $\mathcal{O}(M^2 \log(M))$  with an added  $\mathcal{O}(S)$  step for discretisation of each source. The resulting run time is  $\mathcal{O}(S + M^2 \log(M))$ , which is faster than the direct method of  $\mathcal{O}(M^2S)$  for large values of S.

The FFT, while faster, leaves the resultant image-plane slightly distorted owing to the cyclic nature of the FFT, which causes PSF *side-lobes* to wrap around the image. Additionally, the gridding step (discretisation) intrinsically distorts the input data thus causing slight aliasing in the resultant image (Thompson et al., 2009). Almost all FFT implementations use some form of padding to alleviate the cyclic *ringing* and a post-process to reduce the aliasing caused by the gridding process (Thompson et al., 2009; Taylor et al., 1999).

#### 2.1.3 Simulating Point Source Visibilities

Image synthesis is the act of transforming visibilities to a sky intensity map. The reverse process — producing visibilities using a sky intensity map — is called *visibility simulation*. Simulated visibilities are important for testing (and understanding) instrumental models, something that is necessary to increase signal-to-noise ratios and to obtain more reliable and sensitive data (Smirnov, 2011d).

In order to simulate visibilities, we need a sky intensity map upon which an inverse Fourier transform can be performed. The simplest methods use a sky intensity map comprising a collection of *point sources*, as this requires a simple Fourier transform (Gaussians can also be used). In the MeqTrees software suite, PSVs are computed with a direct Fourier transform (Smirnov, 2012). Theoretically, a sky map can be discretised (or gridded) and use an FFT to obtain the visibilities. This discretisation of data and the effects of this are in early stages of exploration. Appendix B gives a detailed breakdown of the PSV equation.

PSV data changes depending on the layout of the interferometer, the measured frequency bands, the number of time intervals, and the point source model of the sky. Increasing the number of receiving elements in the telescope array results in more visibilities but comes with a concomitant quadratic increase in the processing required to calculate visibilities. For an N element interferometer simulating P point sources, the number of visibilities to be calculated is

$$S = \frac{N(N+1)}{2} \times P \times f \times t$$

where f is the number of frequency channels and t the number of time-steps taken.

Each one of these visibilities V must be described in terms of which antennae pair they derive from, q and q, at what time is was measured, t and the frequency channel, f. This equation, called the Radio Interferometric Measurement Equation (RIME) is derived from the antennae voltages at time t. While the classic RIME is defined in detail in Appendix A, its formulation made it difficult to extent to take into account various noise models, a more modern and flexible model has been developed (Smirnov, 2011a,b,c,d) and reads:

$$V'_{pq}(t,\nu) = \sum_{s} \operatorname{sinc} \frac{\Delta \Psi(\nu_{m})}{2} \operatorname{sinc} \frac{\Delta \Phi(t_{m})}{2} K_{sp}(t,\nu) B_{s} K_{sq}^{H}(t,\nu)$$

$$= \sum_{s} \operatorname{sinc} \frac{\Delta \Psi(\nu_{m})}{2} \operatorname{sinc} \frac{\Delta \Phi(t_{m})}{2} B_{s} e^{-2\pi i \frac{\nu}{c} (\mathbf{u}_{tpq} \boldsymbol{\sigma}_{s})}$$

(2.4)

where  $V_{pq}(t,\nu)$  is complex visibility between antennae p and q at time t in frequency channel f. Other terms in this equation are explained in full in Appendix C.

#### 2.1.4 MeqTrees

MeqTrees (Noordam and Smirnov, 2011) is a software package used for so called third generation calibration (3GC) of radio interferometers and the reverse problem of visibility simulation. In general, it is a software package for calculating any Measurement EQuation specified as an Expression Tree. A measurement equation is an equation that relates the measured signal to the observation. This is covered in more detail in Chapter 4. Expression trees are defined by the user with Python scripts, making MeqTrees easy and flexible to use for most radio interferometric calculations. MeqTrees has been used extensively for LOFAR, WSRT, and MeerKAT and is planned for use in the SKA (Noordam and Smirnov, 2011).

This thesis focuses on the implementation of a MeqTrees 'node' that calculates PSVs. A CPU version of this node already exists in the MeqTrees framework and it is this node against which our GPU results are bench-marked. This 'PSV node' is based on the Radio Interferometry Measurement Equation (RIME), which is detailed in Appendix B.

#### 2.1.5 Parallelism Opportunities

In both image synthesis and visibility simulation, we see similar characteristics. Both perform a Fourier transform for each of the pixels/visibilities that need to be calculated. Indeed, the actual equation of each is the Fourier inverse of the other. For each case all the calculations are the same, but with different input data. This lends itself to a solution employing the Single-Instruction-Multiple-Data (SIMD) paradigm (Patterson and Hennessy, 2008).

Within the domain of high performance parallel computing, there are several ways to approach SIMD problems, most of which require the use of specialised hardware such as Cell (Gschwind, 2006), ClearSpeed (ClearSpeed Technology Ltd, 2012; Kozin, 2009), and MD GRAPE (IBM Research; SGI Japan). These solutions can be very expensive involving high initial investments, specialised maintenance, and often high power-consumption rates (Matsuoka et al., 2009). In 1999 nVidia coined the term Graphics Processing Unit (GPU) to describe the first graphics card in its GeForce range, the GeForce 256 (nVidia Corporation, 1999). Advancements in GPU technology culminated in 2006 when nVidia released its Computer Unified Device Architecture (CUDA) devices (nVidia Corporation, 2006). CUDA exposes the powerful computation ability of the GPU by allowing the user to control the GPU with general code (nVidia Corporation, 2011b) rather than with graphics operations, as had previously been the case (Owens et al., 2008). With lower entrance costs, less specialised maintenance, and reduced power consumption (Matsuoka et al., 2009), CUDA has opened up the field of General Purpose computing on the GPU (GPGPU). Other stream processing technologies are available, for example OpenCL (Munshi, 2011), ATI's Close to Metal (CTM) (Hensley, 2007), AMD's FireStream (AMD, 2010), and MicroSoft's DirectCompute (Microsoft Corporation, 2010). Many of these technologies over generalise the GPU hardware so that it is not fully utilised or are still coming into full maturity as a useful API for GPGPU computing (Karimi et al., 2010).

Our selected HPC platform is commodity nVidia GPGPU system for its effective cost to processing power compared to other systems that require large initial and continued maintenance costs, it's SIMD processing model and because of nVidia's mature API and framework compared to other similar GPGPU technologies, as discussed in Section 1.1.

## 2.2 Graphics Processing Units

Graphics Processing Units (GPUs), or 'graphics cards', were developed for the computer gaming industry, where many pixel and vertex operations must be performed in parallel to render a 3D scene with detailed geometry at an adequate rate (Owens et al., 2008).

Initially, these processors could only perform fixed rendering operations and specific 3D geometry transformations, i.e. to transform 3D vertex information into 2D screen pixel fragments. Fixed processors were later extended into programmable shaders, which enabled programmers to control the GPU via OpenGL or DirectX API calls (Peercy et al., 2000). Shader code allows programmers to choose how a vertex is transformed (with a vertex shader) and how the final pixel stream is drawn to the screen (with a fragment shader). Shader-based graphics cards often have multiple shader processors to improve performance as there are many vertices and fragments on which to operate, but only one vertex and fragment shader program. This Single-Instruction-Multiple-Data (SIMD) model is central to all modern GPU devices.

Initial attempts to leverage shader processors to do general purpose computation on the GPU (GPGPU) demonstrated impressive computational gain. Unfortunately performing such computation requires general code to be written in the guise of rendering operations using graphics primitives such as polygons, textures, and fragments. This adds an unnecessary level of abstraction that the programmer has to account for, involving unintuitive render operations and multiple shader processors with different characteristics. Memory management is arguably even harder, as the programmer had little or no access to the underlying memory hierarchy of shader based GPUs (Buck et al., 2004).

Attempts to abstract these operations were first successfully implemented in the *BrookGPU* API (Buck et al., 2004). BrookGPU converts *Brook language* code into Cg code, a shader language, that can be executed on any hardware that is OpenGL or DirectX compatible.

The disparate shaders were eventually unified into a single, more general, highly parallel type of processor that subsumed all of the shader tasks. This was called the *unified* shader model and modern GPUs contain large numbers of these processors. As a result there is increasing interest in harnessing these low-cost devices for more general purpose computing. The unified shader model allowed for more modern APIs, such as OpenCL (Open Compute Language) (Munshi, 2011). OpenCL abstracts code to be run on a variety of HPC platforms, including multicore CPUs, Intel's Cell processors and most GPUs. Both nVidia and ATI

have released OpenCL implementations for their respective GPU lines.

Besides OpenCL, the two major GPU vendors (nVidia and AMD) have each released their own APIs and GPU compilers for their respective hardware. Unlike OpenCL, these APIs are developed in-house and thus are better able to utilise the specific hardware characteristics of their respective devices. nVidia's CUDA is a standalone API that runs on proprietary nVidia CUDA-enabled GPUs, and like OpenCL it uses a SIMD model for general purpose computation. CUDA is written in a C-like language which is interoperable with standard C and C++ but has bindings and libraries for many other languages. ATI released Close-to-Metal (Hensley, 2007), a low-level programming interface that allows programmers to access low-level instructions of ATI GPUs. This developed into FireStream (AMD, 2010), released by ATI's successor AMD. Both these ATI/AMD technologies were short-lived and current GPGPU efforts from AMD are focused on its OpenCL SDK.

More recently, nVidia has also released an OpenCL SDK, which with sufficient tweaking, is no slower than standard CUDA code (Karimi et al., 2010). Even though these tweaks are CUDA specific (and will not run as fast on an AMD device, for example), this shows promise for OpenCL as a heterogeneous HPC framework that is able to exploit various devices to their full ability. Nevertheless, at the beginning of this thesis, CUDA was clearly the best GPGPU technology available.

Although OpenCL has improved significantly, CUDA remains the more widely used technology owing to its mature API and wide support in the form of libraries and tools. For example cuFFT for Fast Fourier Transforms, cuBLAS for Basic Linear Algebra Solutions, NPP (nVidia Performance Primitives) for image and video processing and many others largely geared at mathematical and statistical problem solving (nVidia Corporation, 2012c). A recent development incorporated in the official CUDA SDK is *Thrust*, a productivity-based CUDA library which generalizes many common CUDA problems into easy-to-code C++ function calls (Hoberock and Bell, 2012; nVidia Corporation, 2011a,b, 2012c). While Thrust is not as efficient as a custom-made CUDA code in terms of GPU utilisation and memory usage, it takes good advantage of CUDA hardware and in most cases is far easier to code than custom CUDA code.

CUDA is able to achieve significant performance owing to its use of many lightweight threads, which run on its many *compute cores*. Standard CPU threads (such as POSIX threads) are run on multi-core systems with each core executing one thread at a time. If there are more threads than cores, active threads can be switched in turn with inactive ones. This form of

thread switching required a costly context switch. A thread's context differs from system to system but all contain at least a set of register values and an instruction pointer. Essentially, the thread's context consists of all the information needed by the thread to continue executing after it has been inactive. CUDA's thread model schedules many thousands of threads and runs these in groups of 32. The 32 thread groups (called warps) run in lock-step on multiple CUDA cores. This is in contrast to CPU threads which run independently on each core; and whose contexts, once started, resides in on-chip memory until the threads have finished execution.

Characteristics of CPU threads include expensive but infrequent context switches and memory latency hiding by use of multiple levels of cache on each CPU core. This model allows for what is called *task-parallelism*, as each thread can execute its own task independent of any other thread's task. In contrast, CUDA threads are characterised by limited caching ability but instantaneous and frequent context switches to hide memory latency, and although they are able to execute on blocks of data per clock cycle, they have limitations when it comes to executing divergent code. CUDA threads exhibit what is called *data-parallelism* as it is suited to computation of a single task upon many data points.

Chapter 3 goes into more detail on the CUDA programming and hardware models, the Thrust library, and common CUDA optimisation techniques.

CUDA FFT implementations: Owing to the importance of the Fast Fourier Transform (FFT) algorithm to the scientific community, HPC implementations of the FFT have been explored using shader based GPUs (Moreland and Angel, 2003), Field Programmable Gate Arrays (FPGAs) (Duan et al., 2011), and OpenCL (Li et al., 2011). There has been extensive interest in porting the FFT to CUDA, and many focus areas have been explored within this sub-field: precision (Govindaraju et al., 2008; Qi et al., 2011), heterogeneous CPU-GPU implementations (Ogata et al., 2008), large-scale FFTs (Chen et al., 2010), 3D FFTs (Nukada et al., 2008), and tuning schemes to yield as much performance as possible (Gu et al., 2010; Dotsenko et al., 2011).

CUDA in Astronomy: Within the field of astronomy, GPGPU technology has already been used to accelerate computationally intensive algorithms (Thompson et al., 2009). For example, a CUDA GPU implementation of gravitational lensing calculations runs roughly two orders of magnitude faster compared to a single core CPU implementation (Bate et al.,

#### CHAPTER 2. BACKGROUND

2010). Monte Carlo dust temperature simulations by Jonsson and Primack (2009) produce speed-ups of up to 69 times over the CPU using CUDA hardware. Ford (2008) used CUDA hardware to accelerate calculations of Kepler's Equation for Exoplanet Searches and obtained speed-ups also in the  $100 \times$  range, approximately. More recently, Clark et al. (2011) utilises 79% of modern GPU's theoretical bandwidth for cross correlation calculations.

Although GPGPU techniques for calculating Fast Fourier Transforms (FFT) have been widely explored, there seems to be little research on GPGPU calculations of direct Fourier transforms.

## 2.3 Summary

This chapter outlines radio interferometry and how an interferometer (an array of radio dishes) is used to produce an image of the sky. Simulating direct interferometer output from a model image is known as *Point Source Visibility* (PSV) simulation and is an important procedure in the calibration loop; however, it is very computationally expensive. Fortunately, PSV simulations follow an SIMD paradigm, which is well explored in high performance computing technology.

In particular GPGPU technology has shown itself to be effective in accelerating SIMD problems, with the added advantage of low entry and maintenance costs associated with commodity hardware.

It follows that radio interferometry PSV calculations can benefit from GPGPU technology and techniques in terms of performance gain as well as cost effectiveness.

## Chapter 3

## **CUDA**

Modern GPUs possess a large number of simple Single-Instruction-Multiple-Data (SIMD) processors that can be harnessed for general purpose computing. In recent years, this task has been made easier with the development of general application programming interfaces for GPUs such as nVidia's *Compute Unified Device Architecture* (CUDA) technology, an SIMD model for general-purpose computation on nVidia commodity GPU hardware (Hoberock and Bell, 2012; nVidia Corporation, 2011a,b).

This chapter introduces CUDA device hardware, memory, and execution model. CUDA's unique execution centres around the use of its many lightweight threads. How these threads are executed on CUDA hardware and how they access the CUDA memory hierarchy is explained. This will give the detailed information needed to make sense of the optimisations and considerations explored in the design and implementation of our PSV node.

## 3.1 CUDA Programming Model

CUDA supports a C-like syntax for its code that is interoperable with standard C and C++. CUDA code is compiled and then 'deployed' to a CUDA capable device. The code is scheduled for execution by thousands of lightweight threads. These threads are divided amongst the device's many compute cores. Although it is claimed that CUDA code is designed to run on any CUDA capable device, in reality this is only partially true. A CUDA GPU has a compute capability (CC), (1.0, 1.1, 1.2, 1.3, 2.0 or 2.1) with each CC generation backwards compatible with devices of a lower CC (for example a CC 2.1 device will run code designed

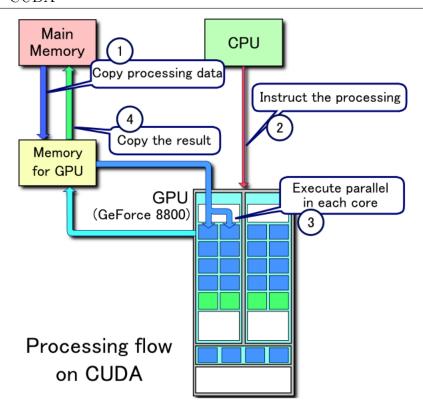

Figure 3.1: CUDA Processing Flow

This is a canonical example of CUDA processing flow. First, data that is to be processed is copied to the GPU device. CUDA code is compiled by the CPU and emphdeployed to the GPU and then executed in parallel on the many compute cores. The processed data is then copied back to the CPU.

for a CC 1.3 device). Devices with CC 1.3 or greater have double precision floating point operations. CC 2.x introduced automatic global memory caching and faster double precision operations (only half the speed of single precision performance, as opposed to 1.x devices which only have one-eight double precision performance).

The CUDA architecture defines two hardware abstractions: the *device*, which is a CUDA-enabled GPU, and the *host*, which is the machine on which the device resides. In order to execute code on the device, a C-like function (called a *kernel*) is executed or invoked. The kernel executes simultaneously on the many lightweight threads of the CUDA device. Data needs to be transferred to and from the device before and after, respectively, executing a kernel function (as shown in Figure 3.1).

There are two main considerations to a CUDA implementation: how data is transferred (memory management) and how this data is operated on (execution model). Unlike CPUs,

which use multiple levels of cache to hide memory access latency (and hence to ensure the processor is always being utilised), CUDA relies on its many lightweight threads and instantaneous thread context switching to swap between threads that are waiting for memory access requests and threads that require processing. This leads to scheduling characteristics and a memory hierarchy that contrasts sharply with a traditional multi-core CPU system.

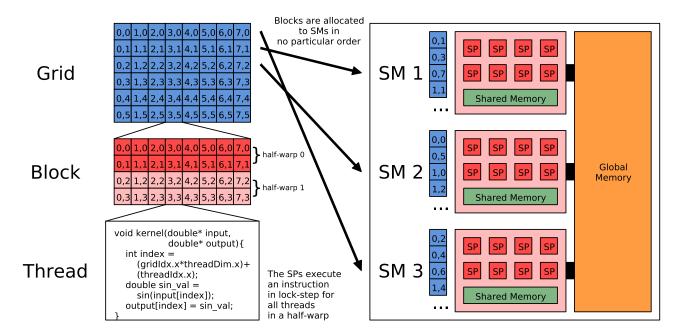

#### 3.1.1 The CUDA Execution Model

To understand the CUDA execution model, we first need to understand how GPU hardware and software components interact and how GPU instructions are scheduled. While seemingly unintuitive at first glance, the CUDA software model mirrors the characteristics of the hardware. Multiple schedulers are used to quickly switch between the many runnable threads. Threads are grouped into blocks and blocks are arranged into a grid. The hardware contains a number of Streaming Multiprocessors (SMs) that will be assigned a number of blocks. The SM is then responsible for scheduling execution of all the threads of all its blocks. The user does not control the schedulers directly, but has full control over the thread and block layout. These layouts along with other factors, explained below, allow the programmer to indirectly but deterministically affect efficient GPU utilisation.

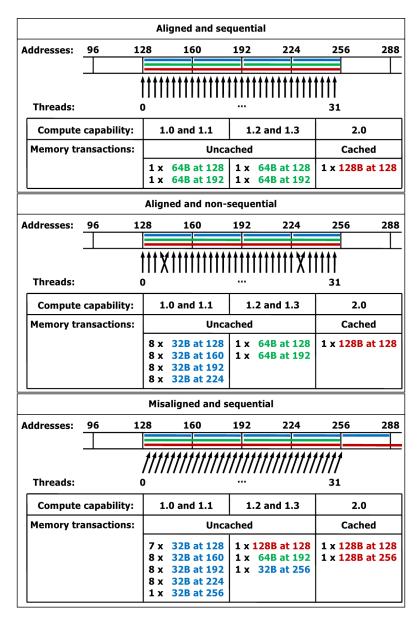

Software Hierarchy - The Grid, Blocks, and Threads: CUDA code defines C-style functions called *kernels*, which are executed in parallel by thousands of lightweight threads on the many cores of the CUDA GPU. Threads are grouped into blocks, with up to 512 (CC 1.3) or 1024 (CC 2.x) threads per block. Blocks are grouped into a grid, which contains up to 65535×65535 × 65535 blocks. Figure 3.2 shows an example grid/block layout. The execution of each block is independent of any other block, with no guarantee of block execution order and no direct mechanism for inter-block communication. Threads within the same block can communicate via *shared memory* (see Section 3.1.2).

Thread-Block Layout and Indexing: Blocks of threads are organised in 1-, 2-, or 3-dimensions and will be interchangeably referred to throughout as *blocks* or *thread-blocks*. Each thread-block dimension can be any size within certain CC specific limitations, but may not exceed 512 (CC 1.3) or 1024 (CC 2.x) threads per block. The grid (of thread-blocks) is also organised into 1-, 2-, or 3-dimensions. Grid dimensions can be any size up to 65535,

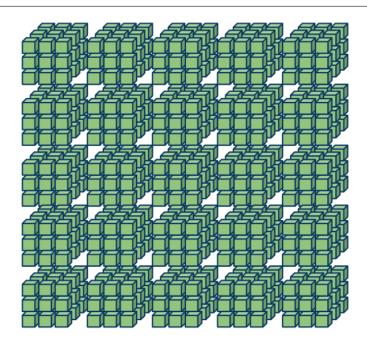

Figure 3.2: Example Grid/Block Layout

In the above, each green cube represents a thread. In this case, there are  $5 \times 5 = 25$  blocks. Each block contains  $3 \times 3 \times 3 = 27$  threads.

meaning that a total of 65535<sup>3</sup> blocks can be held in a grid. The layout of the grid is simply a programming convenience since, as will be seen below, blocks are scheduled on an SM in an undefined order. The block layout, however, can have significant effects on performance.

When a kernel is run, all the threads will run the exact same CUDA code. Thread indexing is thus vital in controlling a specific thread's execution path and the data it operates on. CUDA exposes two important variables, threadIdx and gridIdx, to allow the program to determine which thread from which block is currently undergoing execution. CUDA also uses blockDim and gridDim variables to determine the block and grid layout. Listing 3.1 shows an example CUDA kernel that squares all the values of a  $(512 \times 512)$  array. If the programmer were to specify a thread-block size of, say,  $(8 \times 4)$ , they would need to specify a  $(64 \times 128)$  grid. As standard CUDA arrays are 1-dimensional only, a multi-dimensional array would need to be flattened into a 1D array. Standard arrays are stored in global memory that resides on the DRAM of the GPU (see Section 3.1.2 for details). There are, however, non-global memory types available in CUDA which allow for multi-dimensional array access.

```

__global__ ExampleKernel(float* array, float w, float h) {

// find index of this thread

int indexX = threadIdx.x + (blockIdx.x*blockDim.x);

int indexY = threadIdx.y + (blockIdx.y*blockDim.y);

// we need to work out the flattened index for the flattened array

int flattenedIndex = indexX+(indexY*w);

// we read the value from the array, square it, and write it back

float value = array[flattenedIndex];

array[flattenedIndex] = value * value;

}

```

**Listing 3.1: Example CUDA Kernel**

This CUDA kernel will take a  $w \times h$  flattened array and square its values.

Hardware - The GPU, Streaming Multiprocessors, and Cores: The CUDA execution model arose directly from the design of the CUDA hardware. A CUDA GPU contains a number of *Streaming Multiprocessors* (SMs), each comprising a number of scalar processors (SPs) or *cores* (either 8, 32, or 48 cores per SM). There is thus a direct mapping between the GPU hardware and the software components of CUDA: GPU-device to grid, SM to block, SP/core to thread (Figure 3.3).

nVidia's CUDA GPU cores were developed, in part, by combining vertex, geometry, and fragment shaders into a unified shader unit capable of executing all the necessary shader functionality. This unified shader unit became a single 32bit scalar processor — a CUDA compute core. These cores are organised into groups of 8 (CC 1.x), 32 (CC 2.0) or 48 (CC 2.1) and collectively define a Streaming Multiprocessor (SM).

Any CUDA architecture will include a number of SMs, each being largely independent of any other SM (nVidia Corporation, 2011b). This allows a CUDA GPU to scale by simply adding more SMs to the GPU chip. Indeed, the principal difference between low-end and high-end GPUs of the same series is usually the number of SMs on the chip and the amount of on-board DRAM.

Each SM contains a number of CUDA cores and a number of special function units (SFUs). These SFUs allow CUDA cores access to fast calculation of square-root, exponential, sine, co-sine, and other commonly used mathematical operations. Each SM also has banks of shared memory, cached constant memory, and local registers that are shared between its cores. SMs

Figure 3.3: Thread/Block/Grid hierarchy relation to the GPU/SM/SP hierarchy